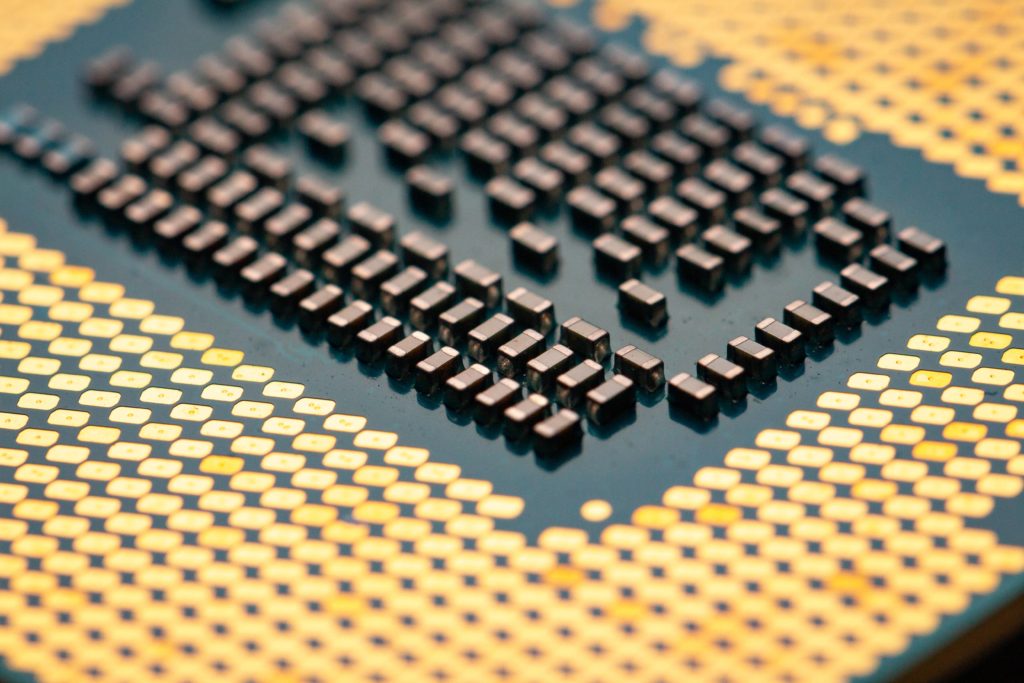

Photo by Kvistholt Photography on Unsplash

THE IMPACT OF CLOUD IN SEMICONDUCTOR INDUSTRY

In the high-tech industry, software plays a crucial role. The ability to manage the task with a click of a button has a profound effect on different day-to-day activities. Software-driven digitization is also a key enabler in achieving productivity, which in turn allows companies/industries to capture the market worldwide.

Over the last few decades, the software delivery model has evolved. From desktop to browser to smartphone apps to cloud, the different software delivery models have increased productivity. Industries worldwide have realized the potential of software-driven solutions and have rightly adopted strategies to maximize software deployment via the cloud. The same is true for the semiconductor industry.

An advanced industry like semiconductor, where a single mistake can amount to zillions of dollars in losses, certainly needs solutions that can help plug any gaps in the product development process. These solutions can range from both the technical and business aspect of the product life cycle.

To achieve high design and manufacturing standards, the semiconductor industry also has been heavily relying on cloud-based software solutions. This is why over the last couple of decades all major segments of the semiconductor industry have adopted cloud strategy.

There are certainly cases where the transformation is happening today, but irrespective of the digital transformation journey, semiconductor design, and manufacturing houses realize the importance of hoping on to the cloud solutions and take advantage of every detail by capturing and connecting all the possible data points.

There are numerous ways in which cloud strategy is impacting the semiconductor industry:

Optimization: To track all the project and product details, cloud-based solutions play a vital role. The tools provide an ability to capture every change (technical and business) and ensure that the information is available on the go. This way of capturing the details allows optimized operations that ensure that the design to manufacturing flow is well connected to the specifications and the execution flow.

Defect And Error Free: By making use of smart and connected equipment with cloud-powered data analytic tools, semiconductor companies can ensure that the end product is defect-free. Deploying smart cloud tools that can capture gaps in the process/recipe ensures that there are no errors in the manufacturing flows.

On-Time: Delivering products on-time to the customer is key to capturing the large market, and it often requires swift coordination between multiple cross-functional teams. To connect and share the information seamlessly needs cloud-powered data-backed solutions that can track every detail from forecasting to material handling. Capturing the minutest of the details ensures that the product reaches the end customer on time.

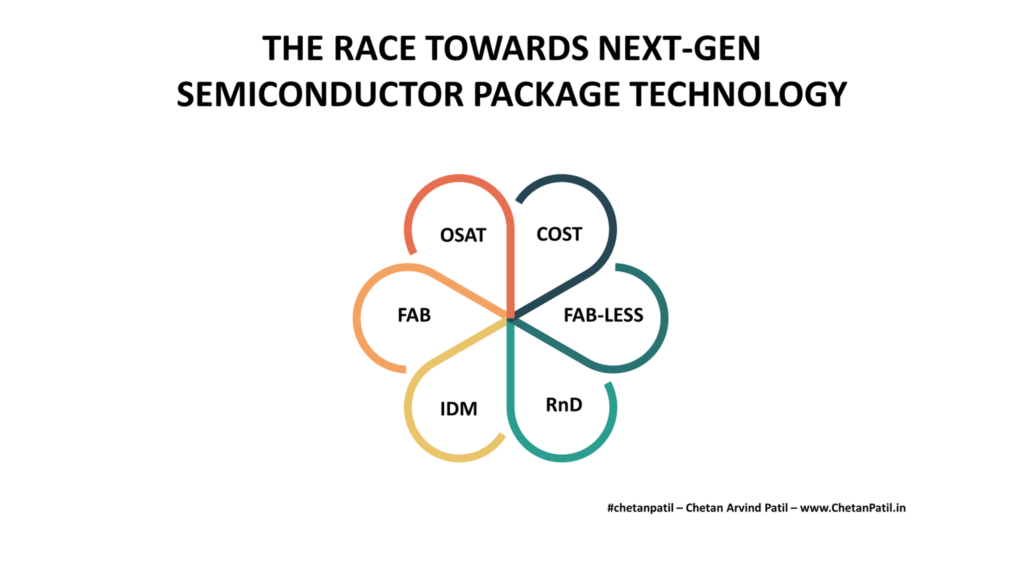

End-To-End Process: Semiconductor industry is built on top of several segments, which includes the design houses to equipment manufacturers to FABs to manufacturing OSAT sites, and many more. All these individual segments should be connected end-to-end to provides a holistic view of how the product development, manufacturing, and delivery flow. This is where cloud-based solutions are useful, and such solutions also bring transparency.

To create a robust and high-quality semiconductor product, numerous data points are required. This is possible only with the help of tools and solutions that connect and provide a detailed view of different stages of the product development cycle. This is why a cloud-based end-to-end solution is heavily used in the semiconductor industry.

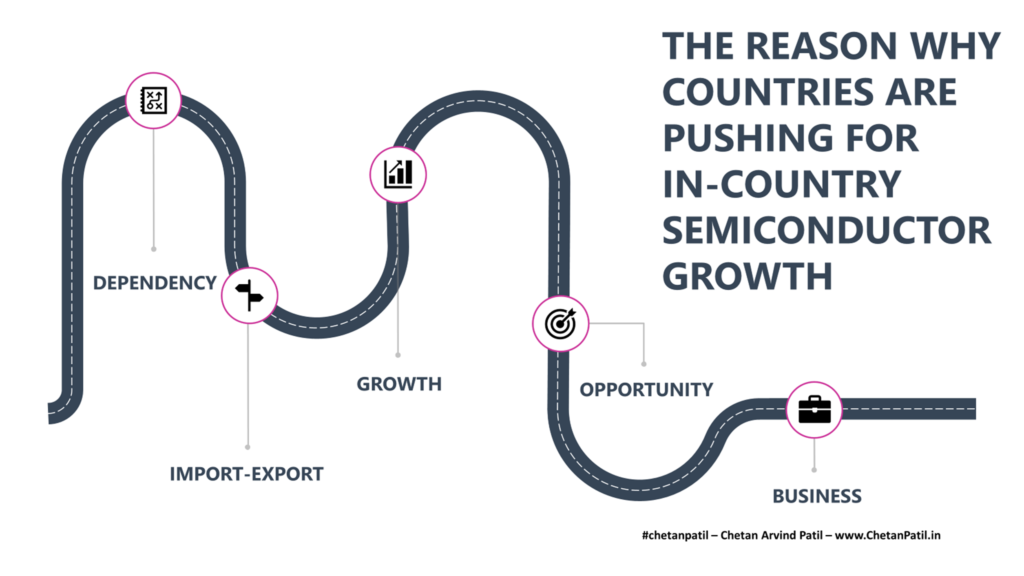

As more FABs and OSATs get established in different parts of the world, the cloud strategy should be one of the top priorities. Doing so, will only increase productivity and enable a better customer experience.

THE USE OF CLOUD IN SEMICONDUCTOR INDUSTRY

Cloud-based solutions are used at every step of semiconductor product development. The efficiency and productivity such tools bring to different stages of product development, ensures that the end-product is defect-free.

Different segments of the semiconductor product development require a unique cloud strategy. These can range from specific EDA tools to massive data storage instances. In the end, all these data points are connected/tied to a specific product. This way any team from anywhere can access the needed data/information to execute the task at hand.

Research And Development: Designing devices to form the circuits and layouts that will eventually get fabricated into a silicon product, is the first step towards developing a turnkey semiconductor solution. For several years, the semiconductor industry has relied on software-based solutions. In the last decade, the same software has moved from desktop to cloud. This has enabled designers and researchers to access files and libraries on-the-go. On top of that, it has taken away the need to have high-performance systems that were earlier required to carry out tons of simulations. Today, one can simply deploy and get on with other work while the simulations are running on the cloud. Using the cloud, companies can ensure that there is no IP infringement as the check can run on the fly and tools can compare design solutions against the massive poll of cell libraries. All this ensures that the right product is developed by following the industry-standard protocols.

Data Analysis: Data generation occurs at every stage of silicon development. Whether it is simulations in our design stage or fabrication/testing in FABs/OSATs. This is why advanced statistical analysis is carried out on every data point that is generated. Doing so on the fly means deploying solutions that can run closer to the data generating source. Also, if the data source is error-free, then data engineers can question it and take a deeper look by using analytical tools. In both scenarios, highly advanced tools are required. This means making use of cloud-based solutions that are easy to access and are loaded with features to enable accurate data exploration.

Supply Chain Management: Delivering products to the end customer often requires connecting several dots from different systems. This is why supply chain management is needed. It ensures the product and its processes are tracked using the unique bill of materials. This often requires relying on specific cloud-based tools that can swiftly retrieve any information related to the products to provide its full history from inception to delivery. Such a task without cloud tools will certainly invite errors.

Market Analysis: Capturing market trends to understand which products will give maximum profits is key to success. This often requires capturing different data points and then aligning the product roadmap as per the market (which means the customer) requirement. This ensures that the CapEx is diverted towards high revenue products. Such planning and projection are not possible without capturing different data points and customer developments. This is where cloud-based market analysis comes in handy and ensures that the projects are profitable.

Resource Management: Semiconductor equipment, tools, and labs require high CapEx and such investment is viable only if there is a high ROI. To achieve positive ROI, the resources need to be looked after and that requires efficient management. This means periodic maintenance to ensure minimum downtime. For such management, cloud-based solutions are deployed so that whenever tools go down or require maintenance, the data can be captured to raise the alert beforehand.

Factory Operation: Running FABs and OSATs 24×7 is key to ensuring that the facilities breakeven as quickly as possible. This requires capturing second to second activity of every corner of the factory. This is possible only when a connected system is deployed that can raise alarm in case of downtime and also provide remote status of every piece of equipment and tools. Cloud-based solutions already play a key role in this can thus are heavily used by semiconductor FABs and OSATs.

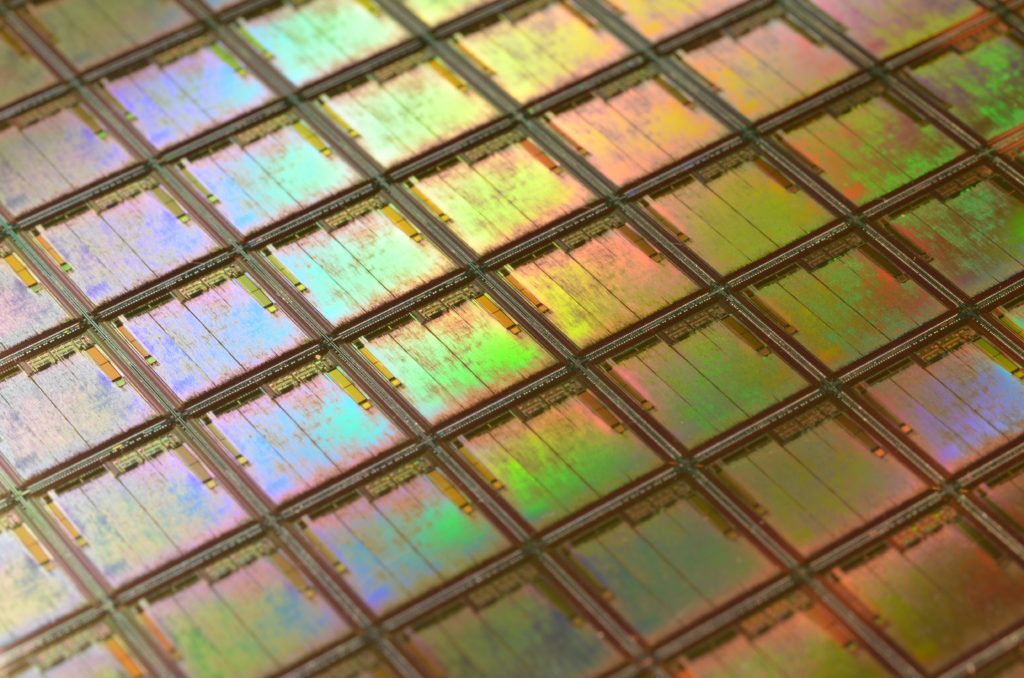

Logistics: Shipping is a big part of the semiconductor product development cycle. The wafers often come from a different outside supplier and then get fabricated at a different location, only to get tested in a different part of the world. This means optimized logistics and real-time tracking of material. While the majority of the logistics solution providers are heavily using cloud-based solutions to track and deliver packages, it so often happens that the semiconductor companies also have to invest internally in systems that can raise shipping labels apart from tracking where the customer deliveries are. This is why cloud-based logistics solutions are handy for semiconductor companies.

Archiving: Saving every data point related to the product is vital. This data ranges from design files to test data to financial records. All these need to be stored for a very long term so that whenever a query or comparison has to be done, the data can be easily retrieved. Quick retrieval and analysis are only possible if cloud solutions are deployed.

The use of the cloud in the semiconductor industry will keep growing. In the next few years, more sophisticated and smart tools will be deployed. Factory operations are already utilizing high-tech cloud solutions for product fabrication. Design and Supply Chain Management are not behind. The cloud market for the semiconductor industry will only keep growing with more new players entering the product development every year.