Image Generated Using DALL-E

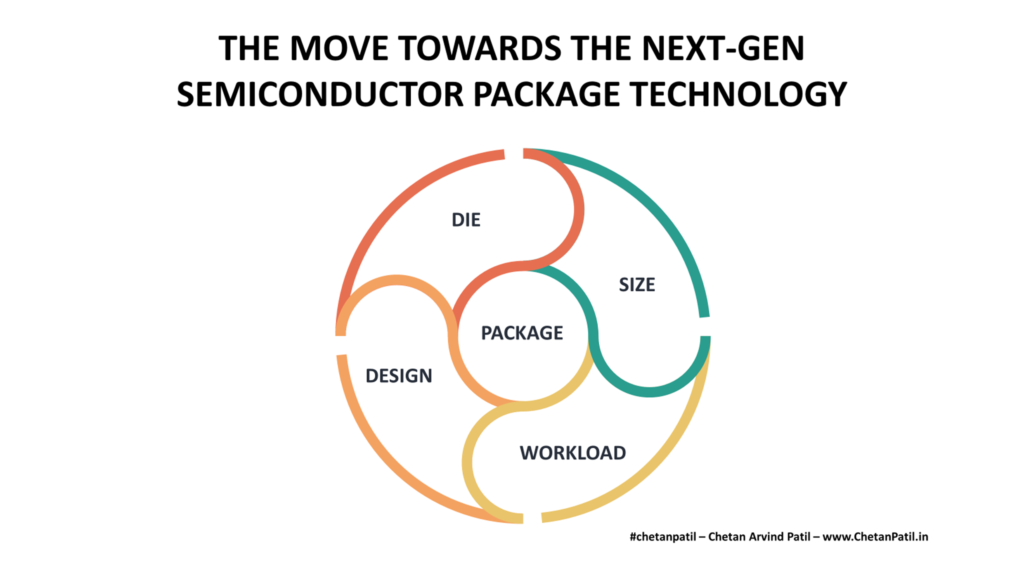

Continuous Package-Level Scaling

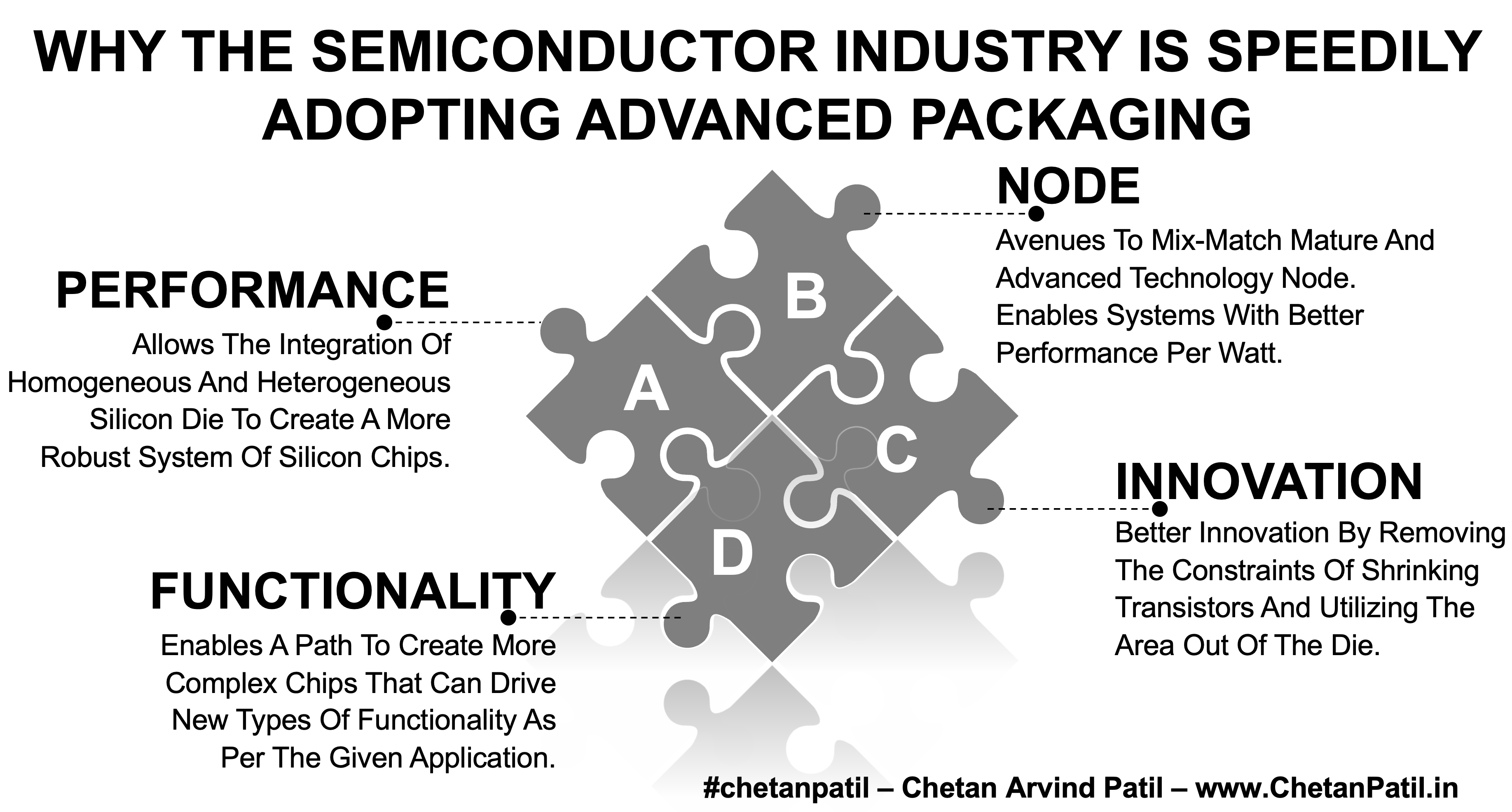

Moore’s Law, which predicted the doubling of transistors every two years, is slowing down due to atomic-scale limitations. The industry is adapting by shifting towards advanced packaging solutions that enable continued performance scaling without the need for extreme lithography advancements, such as EUV (extreme ultraviolet) lithography or multi-patterning techniques.

These new methodologies are not just a shift, but a leap forward in semiconductor technology. They facilitate enhanced chip density, lower power consumption, and higher performance across various applications.

Some of the key package-level scaling approaches include:

- 2.5D and 3D Integration: Stacking chips vertically (3D ICs) or placing them side-by-side on an interposer (2.5D) increases transistor density, enhances bandwidth, and reduces interconnect delays. This approach benefits high-performance computing and AI applications that demand massive data throughput.

- Heterogeneous Integration: Integrating diverse chiplets, logic, memory, RF, analog into a unified package enables optimized performance per function, minimizing power loss and latency while improving efficiency. This allows for tailored architectures that cater to specific workloads, reducing the need for monolithic designs.

- Hybrid Bonding: A next-generation interconnect method that facilitates denser packaging by directly bonding dies at a molecular level, significantly improving performance and reducing power consumption. This approach also enhances signal integrity and minimizes the parasitic effects of traditional interconnects.

- Advanced Thermal Management Solutions: As power densities increase, thermal challenges must be addressed through innovations like embedded microfluidic cooling, thermal interface materials, and optimized heat dissipation structures to maintain system reliability.

- Photonic Integration: The convergence of electronic and photonic components within a package enables ultra-fast optical interconnects, reducing latency and power consumption for data-intensive applications such as AI, cloud computing, and high-speed networking.

This evolution in packaging enhances system-level performance, optimizes power efficiency, and provides superior thermal management, which is critical for AI workloads, high-performance computing, and next-generation consumer electronics.

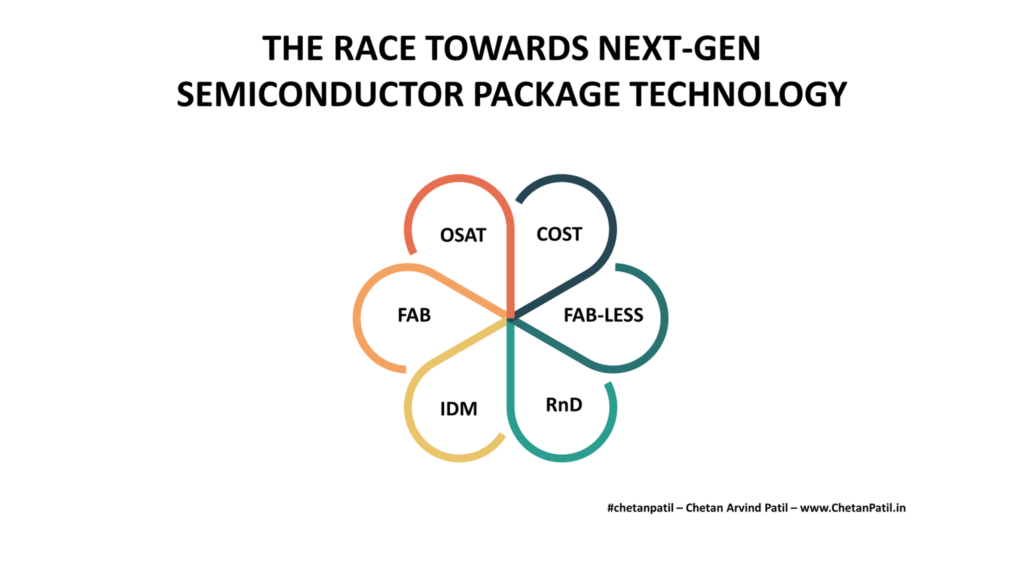

Packaging Cost And Economic Feasibility

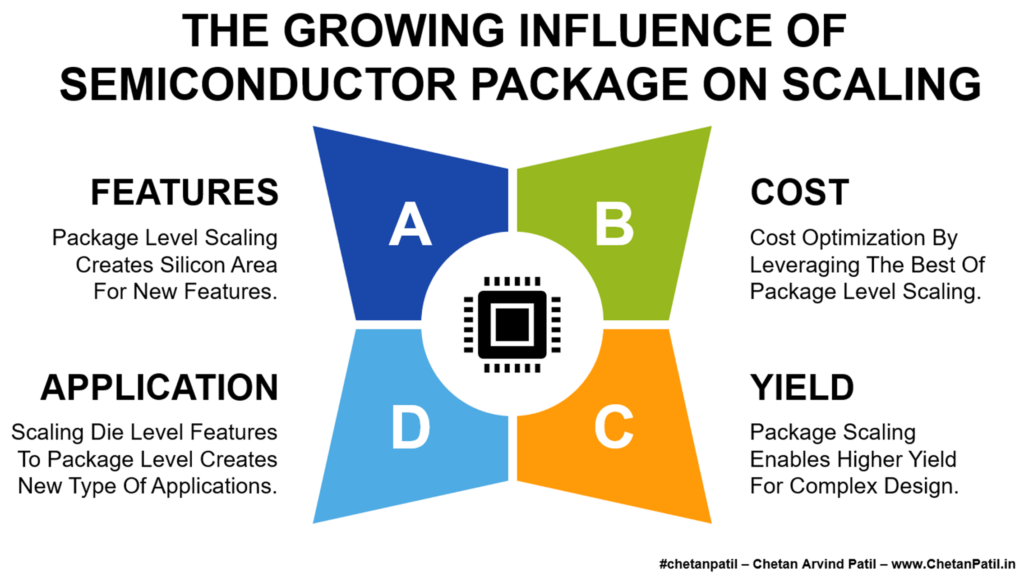

While advanced packaging drives performance scaling, its adoption is increasingly fueled by cost considerations. Traditional monolithic scaling is becoming unsustainable due to rising fabrication costs, process complexity, and diminishing yield efficiency. The heavy reliance on EUV lithography and cutting-edge fabs demands massive capital investments, making continued node scaling economically impractical for many manufacturers.

To mitigate these costs, the industry is shifting toward advanced packaging, which enables performance gains without aggressive transistor scaling. By integrating modular components and optimizing interconnect solutions at the package level, companies can enhance power efficiency, improve yield, minimize material waste, and extend the usability of mature process nodes, all while controlling manufacturing expenses.

The following (few) advanced packaging techniques are enabling this transition by balancing performance with economic feasibility:

- Chiplet-Based Design: Breaking down a large monolithic die into smaller functional chiplets reduces defect rates and improves yield.

- Fan-Out Wafer-Level Packaging (FO-WLP): A cost-efficient alternative to traditional wire bonding, improving I/O density and electrical performance while reducing the package footprint.

- Co-Packaged Optics (CPO): Reducing power consumption and improving data transmission speeds for high-performance computing applications.

- Substrate-Less Packaging: Eliminating the need for an interposer or traditional substrate, which significantly reduces material and production costs.

- Wafer-Level Chip Scale Packaging (WLCSP): Reducing manufacturing complexity by performing packaging steps at the wafer level, which lowers production costs and improves efficiency.

These advanced packaging techniques offer varying trade-offs between cost, performance, and complexity. While some approaches, like chiplet-based design, balance efficiency, and scalability, others prioritize high performance at greater complexity, such as co-packaged optics.

The table below highlights these distinctions, helping to evaluate cost-effective solutions for different semiconductor applications.

| Packaging Technique | Cost Efficiency | Performance | Complexity |

|---|---|---|---|

| Chiplet-Based Design | High | High | Moderate |

| Fan-Out Wafer-Level (FO-WLP) | Moderate | High | Low |

| Co-Packaged Optics (CPO) | Moderate | Very High | High |

| Substrate-Less Packaging | Very High | Moderate | Low |

| Wafer-Level Chip Scale (WLCSP) | Very High | Moderate | Low |

Manufacturability Considerations In Advanced Packaging

The shift to advanced semiconductor packaging demands significant investment in specialized equipment to support complex integration techniques. Hybrid bonding, wafer-level processing, and high-precision lithography require next-generation tools capable of nanoscale accuracy. Advanced metrology and inspection systems are essential to detect defects early and maintain high yields, making capital-intensive upgrades a necessity for semiconductor manufacturers.

Material innovations are also critical in overcoming manufacturability challenges. New substrates, dielectrics, and thermal interface materials are required to enhance interconnect performance, power efficiency, and reliability. High-density redistribution layers (RDLs) and ultra-thin interposers are pushing the limits of traditional materials, requiring ongoing research and collaboration with material science experts.

A skilled talent pool is even more essential to scale advanced packaging technologies. As manufacturing complexity increases, companies must invest in specialized workforce training for precision assembly, hybrid bonding techniques, and AI-driven quality control. Bridging the talent gap requires academic partnerships, internal training programs, and a shift in workforce development strategies to meet the evolving demands of semiconductor packaging.

Finally, investment in infrastructure is critical to ensuring long-term manufacturability. Establishing localized packaging hubs reduces supply chain risks and enables tighter control over production processes. Governments and industry leaders are increasing funding for domestic packaging capabilities to secure technological leadership, reinforcing the strategic importance of advanced semiconductor packaging in the global market.

Takeaway

The semiconductor packaging shift has transcended its conventional role and emerged as a defining factor in the future of chip design and manufacturing. It is no longer just about protecting a chip, it is about unlocking new levels of performance, energy efficiency, and integration essential for the next generation of AI, computing, and high-speed connectivity.

As traditional transistor scaling reaches its limits, the chip design’s ability to innovate depends heavily on the advancements in heterogeneous integration, 3D stacking, and high-bandwidth memory architectures.

Companies that embrace these advanced packaging technologies will position themselves at the forefront of semiconductor progress, driving breakthroughs in areas ranging from mobile computing to AI supercomputing infrastructures. The combined impact of manufacturability enhancements, cost-effective design strategies, and material innovations will determine how effectively the industry can sustain growth while meeting the rising demands for performance and efficiency.

With scaling, economic feasibility, AI-driven architecture, and supply chain resilience shaping the evolution of semiconductor packaging, the industry must recognize that packaging is no longer an afterthought. It is the foundation upon which the next wave of semiconductor breakthroughs will be built, ensuring sustained innovation and competitiveness in an increasingly complex technological landscape.