Image Generated Using 4o

How Large Is The Mature Node Economy

The focus immediately shifts to cutting-edge nodes such as 3nm or 5nm when discussing semiconductors. However, the economic and technological importance of mature semiconductor processes, typically those at or above the 28nm (or 40nm in many cases) node, remains substantial and essential to the industry’s foundation.

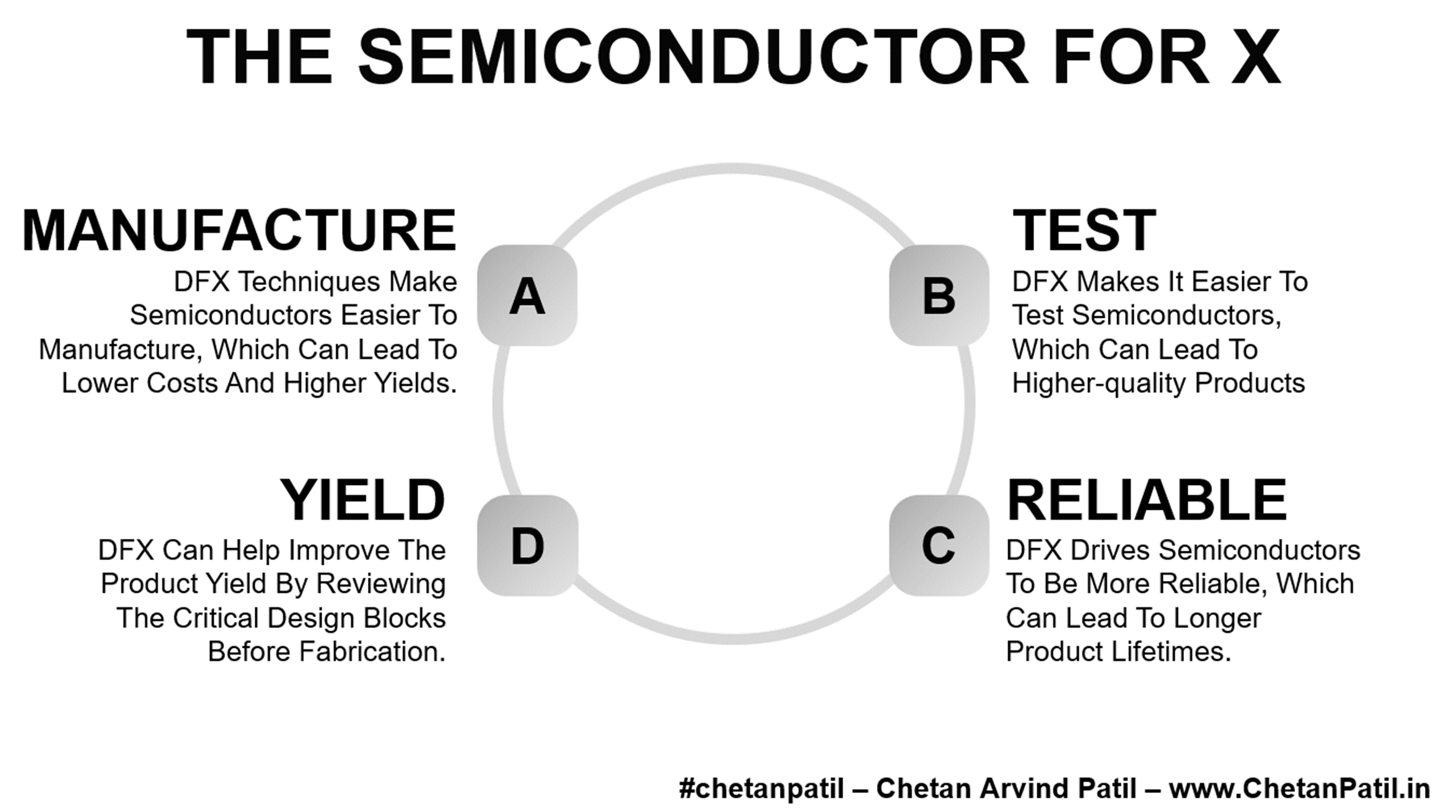

Key technical and economic advantages of mature nodes:

- Cost Efficiency and Equipment Depreciation: Mature semiconductor processes utilize fully depreciated equipment, dramatically lowering capital investment and operational costs compared to advanced-node manufacturing.

- High Yield and Process Stability: Due to extensive operational experience, mature nodes achieve consistently high yields. Process maturity and thoroughly characterized manufacturing steps significantly enhance productivity and reduce variability.

- Established IP and Rapid Qualification: Mature nodes feature extensive intellectual property (IP) libraries and proven design ecosystems, facilitating faster qualification, shorter design cycles, and more predictable product ramps.

These legacy nodes form the critical backbone across numerous essential industries. They drive analog integrated circuits (ICs), power management ICs, automotive microcontrollers, display driver ICs, embedded non-volatile memory solutions, and various sensor-based applications. From a financial standpoint, mature nodes generate a robust, multi-billion-dollar revenue stream, providing economic stability and supporting foundational technologies critical to numerous global industries.

Technical Sweet Spots That Keep Older Nodes Relevant

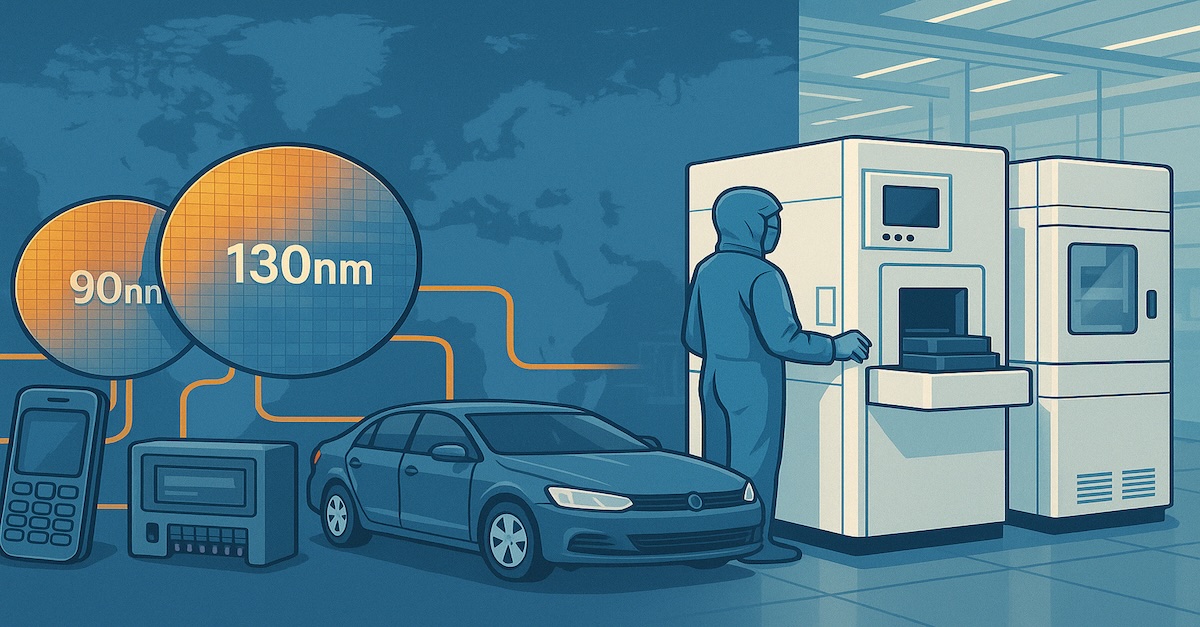

Mature semiconductor nodes possess distinct technical strengths that make them uniquely valuable. They provide specialized features that are challenging or costly for advanced nodes to replicate. Automotive microcontrollers, motor control ICs, industrial controllers, and battery management systems frequently achieve optimal performance within planar CMOS nodes between 40 and 90 nanometers.

Globally, mature-node manufacturing also continues to represent more than half of total wafer output, dominating 200 mm (eight-inch) and 300 mm (twelve-inch) wafer fabs across semiconductor hubs in Taiwan, the United States, Europe, and Asia.

These mature technologies offer robust embedded nonvolatile memory capabilities, delivering high-speed access and extended data retention, which are critical attributes in demanding automotive and industrial environments. Additionally, they leverage thick-oxide transistor designs, which comfortably support voltages above 60 volts, enabling reliable operation in power management and motor control circuits.

Precision analog front-end circuits are another strong suit for older nodes, benefiting from inherently lower noise characteristics and superior linearity thanks to larger transistor dimensions. Integrating these analog functions alongside substantial nonvolatile memory on a single chip significantly reduces complexity and cost, particularly when incorporating similar functionalities within advanced FinFET-based nodes.

Together, these technical advantages solidify mature nodes as the optimal choice for specific use cases where reliability, analog precision, high-voltage handling, and cost efficiency are paramount.

Fresh Money Flows Into Legacy Capacity

Investment and capacity expansion in mature semiconductor nodes are not merely ongoing. They are accelerating significantly. Across the industry, foundries are rapidly scaling their mature-node manufacturing capabilities, with expansions frequently adding tens of thousands of wafers per month to existing facilities. For instance, one prominent foundry is boosting its 28nm, targeting robust demand from the automotive, industrial, and consumer electronics sectors.

At the same time, governments worldwide recognize the strategic importance of mature nodes, resulting in significant financial support. For example, recent government initiatives include a commitment of more than a billion dollar to enhance domestic mature-node manufacturing in the United States, explicitly aiming to bolster capabilities critical for the automotive, industrial, defense, and aerospace sectors.

Similar expansions globally reinforce this trend. European governments have initiated strategic investments in fabs operating between 22 and 180nm nodes to strengthen regional supply chains and ensure technological sovereignty. Meanwhile, joint ventures across the globe (mainly in Asia and EU) are significantly increasing capacity at nodes such as 90nm and 180nm to meet the growing demand for analog and power-management ICs.

Strategic Outlook For Engineers, Investors, And Policy Makers

Older semiconductor nodes are far from obsolete. They represent highly optimized platforms meticulously refined through decades of production experience. These mature nodes deliver exceptional reliability, predictable yield performance, and proven operational stability.

Their inherent cost efficiency, driven by fully depreciated equipment and mature manufacturing processes, makes them economically compelling. Additionally, specialized performance characteristics such as high-voltage handling, precision analog integration, robust embedded memory solutions, and radiation tolerance make older nodes indispensable for specific market segments, including automotive, industrial, and aerospace.

A summarized strategic perspective:

| Stakeholder | Strategic Importance |

|---|---|

| Engineers | Mature nodes provide trusted solutions for analog precision, high-voltage capabilities, radiation tolerance, and embedded non-volatile memory. Extensive IP reuse accelerates design timelines. |

| Investors | Fully depreciated fabs with predictable, stable demand offer attractive margins. Investments have lower risk profiles due to established processes and equipment. |

| Policy Makers | Mature semiconductor processes are strategically essential for national security, automotive resilience, and economic stability. Policy frameworks increasingly treat legacy semiconductor manufacturing as critical infrastructure rather than commodity production. |

Collectively, these strategic considerations confirm that older semiconductor nodes will maintain their critical role well into the next decade, even as the semiconductor industry’s leading edge continues to advance toward ever-smaller technology nodes.